# **RDK X3 Module Design Guide**

v1.0

## **Chapter 1. Introduction**

#### **1.1 References**

Refer to the following list of documents or models for more information. Use the latest revision of all documents.

RDK X3 Module Datasheet

RDK X3 Module Pinmux

RDK X3 Module Thermal Design Guide

RDK X3 Module AVL (Approved Validation List)

This design guide contains recommendations and guidelines for engineers to follow to create a product that is optimized to achieve the best performance from the interfaces supported by the RDK X3 Module.

### **1.2 Abbreviations and Definitions**

Table 1-1 lists the abbreviations that may be used throughout this design and guide and their definitions.

| Abbreviation | Definition                           |  |  |

|--------------|--------------------------------------|--|--|

| CEC          | Consumer Electronic Control          |  |  |

| CSI          | Camera Serial Interface              |  |  |

| Diff         | Differential                         |  |  |

| ESD          | Electrostatic Discharge              |  |  |

| EMI          | Electromagnetic Interference         |  |  |

| FET          | Field Effect Transistor              |  |  |

| GPIO         | General Purpose Input Output         |  |  |

| HDCP         | High-bandwidth Digital Content       |  |  |

| HDCP         | Protection                           |  |  |

| HDMI         | High Definition Multimedia Interface |  |  |

| I2C          | Inter IC Interface                   |  |  |

| I2S          | Inter IC Sound Interface             |  |  |

Table 1-1. Abbreviations and Definitions

| LDO    | Low Dropout (voltage regulator)     |  |  |

|--------|-------------------------------------|--|--|

|        | Low Power Double Data Rate          |  |  |

| LPDDR4 | DRAM, Forth generation              |  |  |

| MDI    | Medium-Dependent Interface          |  |  |

| MIPI   | Mobile Industry Processor Interface |  |  |

| mm     | Millimeter                          |  |  |

| ms     | Milliseconds                        |  |  |

| Abbreviation | Definition                            |  |  |

|--------------|---------------------------------------|--|--|

| РНҮ          | Physical Interface (that is, USB PHY) |  |  |

| ps           | Pico-Seconds                          |  |  |

| PMIC         | Power Management In RDK X3            |  |  |

| PMIC         | Module Circuit                        |  |  |

| RJ45         | 8P8C modular connector used in        |  |  |

| KJ4J         | Ethernet and other data links         |  |  |

| RTC          | Real Time Clock                       |  |  |

| SE           | Single-Ended                          |  |  |

| SoC          | System on Chip                        |  |  |

| SPI          | Serial Peripheral Interface           |  |  |

| TMDS         | Transition-Minimized Differential     |  |  |

| TMDS         | Signaling                             |  |  |

| UART         | Universal Asynchronous Receiver-      |  |  |

| UANI         | Transmitter                           |  |  |

| USB          | Universal Serial Bus                  |  |  |

| MIPI         | Mobile Industry Processor Interface   |  |  |

| eMMC         | embedded MultiMediaCard               |  |  |

| SDIO         | Secure Digital Input and Output       |  |  |

# Chapter 2. RDK X3 Module

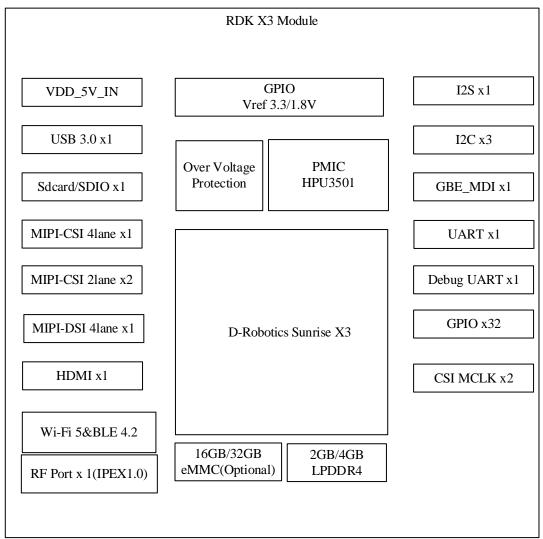

The RDK X3 Module resides at the center of the embedded system solution and includes:

$\Box$  Power (Power sequencer, regulators, and so on)

- DRAM (LPDDR4)

- Gigabit Ethernet PHY

- □ QSPI NAND (Boot device)

- □ eMMC 5.0 (Storage device, Optional)

- □ Wi-Fi&BLE (Optional)

In addition, a wide range of interfaces are available at the main connector for use on the carrier board as shown in Table 2-1 and Figure 2-1.

Table 2-1. RDK X3 Module Interfaces

| Category | Function                           | Category   | Function              |

|----------|------------------------------------|------------|-----------------------|

| 1100     |                                    | LAN        | Gigabit Ethernet (1x) |

| USB      | USB 3.0 (1x)                       | WLAN       | IEEE 802.11a/b/g/n/ac |

| SDIO     | Micro SD (1x)                      | Bluetooth  | BLE 4.2               |

| Camera   | MIPI-CSI (1x4 lanes and 2x2 lanes) | GPIO       | 32x                   |

| Camera   | Control, clock                     | Main Power | 5V DC 3A              |

| D' 1     | HDMI x1                            |            |                       |

| Display  | MIPI-DSI (1x4 lanes)               |            |                       |

Figure 2-1. RDK X3 Module Block Diagram

Table 2-2. RDK X3 Module Connector 200-Pin Pinout Matrix

| Pin | Signal           | Description                                                  |

|-----|------------------|--------------------------------------------------------------|

| 1   | GND              | Ground (0V)                                                  |

| 2   | GND              | Ground (0V)                                                  |

| 3   | Ethernet_Pair3_P | Ethernet pair 3 positive (connect to transformer or MagJack) |

| 4  | Ethernet_Pair1_P | Ethernet pair 1 positive (connect to transformer or MagJack)                                        |  |  |  |

|----|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| 5  | Ethernet_Pair3_N | Ethernet pair 3 negative (connect to transformer or MagJack)                                        |  |  |  |

| 6  | Ethernet_Pair1_N | Ethernet pair 1 negative (connect to transformer or MagJack)                                        |  |  |  |

| 7  | GND              | Ground (0V)                                                                                         |  |  |  |

| 8  | GND              | Ground (0V)                                                                                         |  |  |  |

| 9  | Ethernet_Pair2_N | Ethernet pair 2 negative (connect to transformer or MagJack)                                        |  |  |  |

| 10 | Ethernet_Pair0_N | Ethernet pair 0 negative (connect to transformer or MagJack)                                        |  |  |  |

| 11 | Ethernet_Pair2_P | Ethernet pair 2 positive (connect to transformer or MagJack)                                        |  |  |  |

| 12 | Ethernet_Pair0_P | hernet pair 0 positive (connect to transformer or MagJack)                                          |  |  |  |

| 13 | GND              | round (0V)                                                                                          |  |  |  |

| 14 | GND              | Ground (0V)                                                                                         |  |  |  |

| 15 | Ethernet_nLED3   | Active-low Ethernet speed indicator (3.3V signal): typically a yellow LED is connected to this pin. |  |  |  |

|    |                  | A low state indicates the 1Gbit or 100Mbit link: $IOL = 8mA @ VOL < 0.4V$                           |  |  |  |

| 16 | Debug_Uart0_RX   | Uart Data RX pin:Debug,a 1.8V signal                                                                |  |  |  |

| 17 | Ethernet_nLED2   | Active-low Ethernet speed indicator (3.3V signal): typically a yellow LED is connected to this pin. |  |  |  |

|    |                  | A low state indicates the 1Gbit or 100Mbit link: $IOL = 8mA @ VOL < 0.4V$                           |  |  |  |

| 18 | Debug_Uart0_TX   | Uart Data TX pin:Debug,a 1.8V signal                                                                |  |  |  |

| 19 | NC               |                                                                                                     |  |  |  |

| 20 | NC               | NC                                                                                                  |  |  |  |

| 21 | Pi_nLED_Activity | Active-low Pi activity LED. 20mA Max 5V tolerant (VOL < 0.4V).                                      |  |  |  |

| 22 | GND              | Ground (0V)                                                                                         |  |  |  |

| 23 | GND              | Ground (0V)                                                                                         |  |  |  |

| 24 | GPIO26           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 25 | GPIO21           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 26 | GPIO19           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 27 | GPIO20           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 28 | GPIO13           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 29 | GPIO16           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 30 | GPIO6            | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 31 | GPIO12           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 32 | GND              | Ground (0V)                                                                                         |  |  |  |

| 33 | GND              | Ground (0V)                                                                                         |  |  |  |

| 34 | GPIO5            | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 35 | ID_SC            | (BCM2711 GPIO 1) GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting              |  |  |  |

|    |                  | GPIO_VREF to 1.8V                                                                                   |  |  |  |

| 36 | ID_SD            | (BCM2711 GPIO 0) GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting              |  |  |  |

|    |                  | GPIO_VREF to 1.8V                                                                                   |  |  |  |

| 37 | GPIO7            | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 38 | GPIO11           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 39 | GPIO8            | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 40 | GPIO9            | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 41 | GPIO25           | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V             |  |  |  |

| 42       | GND          | Ground (0V)                                                                                          |

|----------|--------------|------------------------------------------------------------------------------------------------------|

| 43       | GND          | Ground (0V)                                                                                          |

| 44       | GPIO10       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 45       | GPIO24       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 46       | GPIO22       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 47       | GPIO23       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 48       | GPIO27       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 49       | GPIO18       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 50       | GPIO17       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 51       | GPIO15       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 52       | GND          | Ground (0V)                                                                                          |

| 52<br>53 | GND          | Ground (0V)                                                                                          |

|          |              | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 54<br>55 | GPIO4        |                                                                                                      |

| 55       | GPIO14       | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V              |

| 56       | GPIO3        | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V.             |

|          |              | Internal 1.8kΩ pull up to GPIO_VREF                                                                  |

| 57       | SD_CLK       | SD card clock signal                                                                                 |

| 58       | GPIO2        | GPIO: typically a 3.3V signal, but can be a 1.8V signal by connecting GPIO_VREF to 1.8V.             |

|          |              | Internal 1.8kΩ pull up to GPIO_VREF                                                                  |

| 59       | GND          | Ground (0V)                                                                                          |

| 60       | GND          | Ground (0V)                                                                                          |

| 61       | SD_DAT3      | SD card/eMMC Data3 signal                                                                            |

| 62       | SD_CMD       | SD card/eMMC Command signal                                                                          |

| 63       | SD_DAT0      | SD card/eMMC Data0 signal                                                                            |

| 64       | UART2_TXD    | Uart Data TX pin: Internal $4k\Omega$ pull up to GPIO_VREF                                           |

| 65       | GND          | Ground (0V)                                                                                          |

| 66       | GND          | Ground (0V)                                                                                          |

| 67       | SD_DAT1      | SD card/eMMC Data1 signal                                                                            |

| 68       | UART2_RXD    | Uart Data RX pin: Internal 4kΩ pull up to GPIO_VREF                                                  |

| 69       | SD_DAT2      | SD card/eMMC Data2 signal                                                                            |

| 70       | SENSOR0_MCLK | GPIO: typically a 1.8V signal                                                                        |

| 71       | GND          | Ground (0V)                                                                                          |

| 72       | SENSOR1_MCLK | GPIO: typically a 1.8V signal                                                                        |

| 73       | NC           | NC                                                                                                   |

| 74       | GND          | Ground (0V)                                                                                          |

| 75       | SD_PWR_ON    | Output to power-switch for the SD card. The module sets this pin high (3.3V) to signal that power to |

|          |              | the SD card should be turned on. Defaults Output low. If booting from the SD card is required then a |

|          |              | pullup should also be fitted so the power-switch defaults to on.                                     |

| 76       | SD0_DET_N    | GPIO: typically a 1.8V signal                                                                        |

| 77       | +5V (Input)  | 4.75V-5.25V. Main power input                                                                        |

| 78       | GPIO_VREF    | Must be connected to MD_3.3V (pins 84 and 86) for 3.3V GPIO or MD_1.8V (pins 88 and 90) for          |

|          | _            |                                                                                                      |

| 79  | +5V (Input)      | 4.75V-5.25V. Main power input                                                                            |  |  |

|-----|------------------|----------------------------------------------------------------------------------------------------------|--|--|

| 80  | SCL1             | I2C clock pin: typically used for Camera and Display. Internal $4k\Omega$ pull up to MD_3.3V             |  |  |

| 81  | +5V (Input)      | 4.75V-5.25V. Main power input                                                                            |  |  |

| 82  | SDA1             | I2C Data pin: typically used for Camera and Display. Internal $4k\Omega$ pull up to MD_3.3V              |  |  |

| 83  | +5V (Input)      | 4.75V-5.25V. Main power input                                                                            |  |  |

| 84  | MD_3.3V (Output) | $3.3V \pm 2.5\%$ . Power Output max 300mA per pin for a total of 600mA. This will be powered down        |  |  |

|     |                  | during power-off or GLOBAL_EN being set low                                                              |  |  |

| 85  | +5V (Input)      | 4.75V-5.25V. Main power input                                                                            |  |  |

| 86  | MD_3.3V (Output) | $3.3V \pm 2.5\%$ . Power Output max 300mA per pin for a total of 600mA. This will be powered down        |  |  |

|     |                  | during power-off or GLOBAL_EN being set low                                                              |  |  |

| 87  | +5V (Input)      | 4.75V-5.25V. Main power input                                                                            |  |  |

| 88  | MD_1.8V (Output) | $1.8V \pm 2.5\%$ . Power Output max 300mA per pin for a total of 600mA. This will be powered down        |  |  |

|     |                  | during power-off or GLOBAL_EN being set low                                                              |  |  |

| 89  | WL_nDisable      | Can be left floating; if driven low the wireless interface will be disabled. Internally pulled up via    |  |  |

|     |                  | 4kΩ to 3.3V                                                                                              |  |  |

| 90  | MD_1.8V (Output) | $1.8V \pm 2.5\%$ . Power Output max 300mA per pin for a total of 600mA. This will be powered down        |  |  |

|     |                  | during power-off or GLOBAL_EN being set low                                                              |  |  |

| 91  | BT_nDisable      | Can be left floating; if driven low the Bluetooth interface will be disabled. Internally pulled up       |  |  |

|     |                  | via4kΩ to 3.3V                                                                                           |  |  |

| 92  | RUN_PG           | Bidirectional pin. Can be driven low (via a $220\Omega$ resistor) to reset the CPU. As an output, a high |  |  |

|     |                  | signals that power is good and CPU is running. Internally pulled up to 3.3V via $2k\Omega$               |  |  |

| 93  | nRPIBOOT         | A low on this pin forces booting from an RPI server (e.g. PC or a Raspberry Pi); if not used leave       |  |  |

|     |                  | floating. Internally pulled up via $4k\Omega$ to $3.3V$                                                  |  |  |

| 94  | NC               | NC                                                                                                       |  |  |

| 95  | PI_LED_nPWR      | Active-low output to drive Power On LED. This signal needs to be buffered.                               |  |  |

| 96  | NC               | NC                                                                                                       |  |  |

| 97  | Camera_GPIO      | Typically used to shut down the camera to reduce power. Reassigning this pin to another function         |  |  |

|     |                  | isn't recommended. MD_3.3V signaling                                                                     |  |  |

| 98  | GND              | Ground (0V)                                                                                              |  |  |

| 99  | GLOBAL_EN        | Input. Drive low to power off Module. Internally pulled up with a $47k\Omega$ to $+5V$                   |  |  |

| 100 | nEXTRST          | Output. Driven low during reset; Driven high (MD_3.3V) once Module CPU has started to boot.              |  |  |

|     |                  | Internally pulled up via4kΩ to 3.3V                                                                      |  |  |

| 101 | USB_OTG_ID       | Input (3.3V signal) USB OTG Pin. Internally pulled up 4K to 3V3. When grounded the Module                |  |  |

|     |                  | becomes a USB host but the correct OS driver also needs to be used                                       |  |  |

| 102 | NC               | NC                                                                                                       |  |  |

| 103 | USB_N            | USB D-                                                                                                   |  |  |

| 104 | 5V               | 4.75V-5.25V. Main power input                                                                            |  |  |

| 105 | USB_P            | USB D+                                                                                                   |  |  |

| 106 | 5V               | 4.75V-5.25V. Main power input                                                                            |  |  |

| 107 | GND              | Ground (0V)                                                                                              |  |  |

| 108 | GND              | Ground (0V)                                                                                              |  |  |

| 109 | NC               | NC                                                                                                       |  |  |

| 110 | NC               | NC                                                                                                       |  |  |

| 111 | NC        | NC                                                                                             |

|-----|-----------|------------------------------------------------------------------------------------------------|

| 112 | NC        | NC                                                                                             |

| 113 | GND       | Ground (0V)                                                                                    |

| 114 | GND       | Ground (0V)                                                                                    |

| 115 | CAM1_D0_N | Input Camera1 D0 negative                                                                      |

| 116 | USB_RX_P  | USB3.0 RX positive                                                                             |

| 117 | CAM1_D0_P | Input Camera1 D0 positive                                                                      |

| 118 | USB_RX_N  | USB3.0 RX negative                                                                             |

| 119 | GND       | Ground (0V)                                                                                    |

| 120 | GND       | Ground (0V)                                                                                    |

| 121 | CAM1_D1_N | Input Camera1 D1 negative                                                                      |

| 122 | USB_TX_P  | USB3.0 TX positive                                                                             |

| 123 | CAM1_D1_P | Input Camera1 D1 positive                                                                      |

| 124 | USB_TX_N  | USB3.0 TX negative                                                                             |

| 125 | GND       | Ground (0V)                                                                                    |

| 126 | GND       | Ground (0V)                                                                                    |

| 127 | CAM1_C_N  | Input Camera1 clock negative                                                                   |

| 128 | CAM0_D0_N | Input Camera0 D0 negative                                                                      |

| 129 | CAM1_C_P  | Input Camera1 clock positive                                                                   |

| 130 | CAM0_D0_P | Input Camera0 D0 positive                                                                      |

| 131 | GND       | Ground (0V)                                                                                    |

| 132 | GND       | Ground (0V)                                                                                    |

| 133 | CAM1_D2_N | Input Camera1 D2 negative                                                                      |

| 134 | CAM0_D1_N | Input Camera0 D1 negative                                                                      |

| 135 | CAM1_D2_P | Input Camera1 D2 positive                                                                      |

| 136 | CAM0_D1_P | Input Camera0 D1 positive                                                                      |

| 137 | GND       | Ground (0V)                                                                                    |

| 138 | GND       | Ground (0V)                                                                                    |

| 139 | CAM1_D3_N | Input Camera1 D3 negative                                                                      |

| 140 | CAM0_C_N  | Input Camera0 clock negative                                                                   |

| 141 | CAM1_D3_P | Input Camera1 D3 positive                                                                      |

| 142 | CAM0_C_P  | Input Camera0 clock positive                                                                   |

| 143 | NC        | NC                                                                                             |

| 144 | GND       | Ground (0V)                                                                                    |

| 145 | NC        | NC                                                                                             |

| 146 | NC        | NC                                                                                             |

| 147 | NC        | NC                                                                                             |

| 148 | NC        | NC                                                                                             |

| 149 | NC        | NC                                                                                             |

| 150 | GND       | Ground (0V)                                                                                    |

| 151 | HDMI0_CEC | Input HDMI0 CEC. 5V tolerant (It can be connected directly to a HDMI connector; a small amount |

|     |           | of ESD protection is provided on the Module by an on-board HDMI05-CL02F3)                      |

| 152 | NC          | NC                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------|

| 153 | HDMI0_HPD   | Input HDMI0 hot plug. 5V tolerant. (It can be connected directly to a HDMI connector; a small |

|     |             | amount of ESD protection is provided on the Module by an on-board HDMI05-CL02F3)              |

| 154 | NC          | NC                                                                                            |

| 155 | GND         | Ground (0V)                                                                                   |

| 156 | GND         | Ground (0V)                                                                                   |

| 157 | CAM2_D0_N   | Input Camera2 D0 negative                                                                     |

| 158 | NC          | NC                                                                                            |

| 159 | CAM2_D0_P   | Input Camera2 D0 positive                                                                     |

| 160 | NC          | NC                                                                                            |

| 161 | GND         | Ground (0V)                                                                                   |

| 162 | GND         | Ground (0V)                                                                                   |

| 163 | CAM2_D1_N   | Input Camera2 D1 negative                                                                     |

| 164 | NC          | NC                                                                                            |

| 165 | CAM2_D1_P   | Input Camera2 D1 positive                                                                     |

| 166 | NC          | NC                                                                                            |

| 167 | GND         | Ground (0V)                                                                                   |

| 168 | GND         | Ground (0V)                                                                                   |

| 169 | CAM2_C_N    | Input Camera2 clock negative                                                                  |

| 170 | HDMI0_TX2_P | Output HDMI0 TX2 positive                                                                     |

| 171 | CAM2_C_P    | Input Camera2 clock positive                                                                  |

| 172 | HDMI0_TX2_N | Output HDMI0 TX2 negative                                                                     |

| 173 | GND         | Ground (0V)                                                                                   |

| 174 | GND         | Ground (0V)                                                                                   |

| 175 | DSI1_D0_N   | Output Display1 D0 negative                                                                   |

| 176 | HDMI0_TX1_P | Output HDMI0 TX1 positive                                                                     |

| 177 | DSI1_D0_P   | Output Display1 D0 positive                                                                   |

| 178 | HDMI0_TX1_N | Output HDMI0 TX1 negative                                                                     |

| 179 | GND         | Ground (0V)                                                                                   |

| 180 | GND         | Ground (0V)                                                                                   |

| 181 | DSI1_D1_N   | Output Display1 D1 negative                                                                   |

| 182 | HDMI0_TX0_P | Output HDMI0 TX0 positive                                                                     |

| 183 | DSI1_D1_P   | Output Display1 D1 positive                                                                   |

| 184 | HDMI0_TX0_N | Output HDMI0 TX0 negative                                                                     |

| 185 | GND         | Ground (0V)                                                                                   |

| 186 | GND         | Ground (0V)                                                                                   |

| 187 | DSI1_C_N    | Output Display1 clock negative                                                                |

| 188 | HDMI0_CLK_P | Output HDMI0 clock positive                                                                   |

| 189 | DSI1_C_P    | Output Display1 clock positive                                                                |

| 190 | HDMI0_CLK_N | Output HDMI0 clock negative                                                                   |

| 191 | GND         | Ground (0V)                                                                                   |

| 192 | GND         | Ground (0V)                                                                                   |

| 193 | DSI1_D2_N | Output Display1 D2 negative                                                                         |  |  |

|-----|-----------|-----------------------------------------------------------------------------------------------------|--|--|

| 194 | DSI1_D3_N | Output Display1 D3 negative                                                                         |  |  |

| 195 | DSI1_D2_P | Output Display1 D2 positive                                                                         |  |  |

| 196 | DSI1_D3_P | Output Display1 D3 positive                                                                         |  |  |

| 197 | GND       | Ground (0V)                                                                                         |  |  |

| 198 | GND       | Ground (0V)                                                                                         |  |  |

| 199 | HDMI0_SDA | idirectional HDMI0 SDA. Internally pulled up with a $2k\Omega$ . 5V tolerant. (It can be connected  |  |  |

|     |           | irectly to a HDMI connector; a small amount of ESD protection is provided on the Module by an       |  |  |

|     |           | on-board HDMI05-CL02F3)                                                                             |  |  |

| 200 | HDMI0_SCL | Bidirectional HDMI0 SCL. Internally pulled up with a $2k\Omega$ . 5V tolerant. (It can be connected |  |  |

|     |           | directly to a HDMI connector; a small amount of ESD protection is provided on the Module by an      |  |  |

|     |           | on-board HDMI05-CL02F3)                                                                             |  |  |

# Chapter 3. RDK X3 Module Boot Considerations

The RDK X3 Module can boot in two ways:

QSPI – normal operation

USB Recovery Mode - development and production programming

### **3.1 QSPI Boot**

The RDK X3 Module normally boots from QSPI NAND. However, the QSPI's 64 MB of storage is not expected to contain all the files for a fully functioning system. Secondary storage needs to be provided through on-board eMMC or external Micro SD Card.

#### 3.2 USB Recovery Mode

USB Recovery mode provides an alternate mode. In this mode, the system is connected to a host system and boots over QSPI Boot which can entry fastboot mode to burn in new fully functioning system. This is used when a new image needs to be flashed. To enter USB recovery mode, the nRPIBOOT \* pin is held low when the system is powered on.

nRPIBOOT \* is the SoC RCM0 strap

Only USB\_DM/DP supports USB Recovery Mode

No other signals are required or supported for entering Force Recovery mode. If the force recovery strap is held low coming out of reset, RDK X3 Module will configure USB as a device and enter recovery mode.

See the USB section (Section 6.1) for an example figure that shows USB connected to a USB Micro B connector.

## **Chapter 4. Modular Connector**

#### 4.1 Module Connector Details

The RDK X3 Module connect to the carrier board using a 200-pin board-to-board connector. The mating connector used on the reference design carrier board will be listed in the RDK X3 Module AVL (Approved Validation List). The connector listed in the RDK X3 Module is the same, so that document can be referenced. This connector is a board-to-board Connector with 0.4mm Pitch, 1.45mm Height.

#### 4.2 Module to Mounting Hardware

The RDK X3 Module is installed in the board-to-board connector to hold the board. In addition, it is recommended that the module is mounted to the main carrier board PCB using metal screws (or equivalent), both for mechanical integrity and to provide additional grounding points. And if install the heat sink or other thermal solution, the metal screws (or equivalent) are necessary. The recommended screws that match the metal hole on board are M2.0  $\times$  4.0 mm typically, flat head. Other board-to-board connector heights are available. If a different height connector is used, the screw height will have to be adjusted accordingly to account for the difference in height from main carrier board PCB to module PCB.

#### 4.3 Module Installation and Removal Operating Guidelines

To install the RDK X3 Module correctly, follow the sequence and mounting hardware instructions: Here are some suggested assembly guidelines.

1. Install the module

a). Start with baseboard that has suitable clearance room to match board-to-board connector height.

b). Insert module fully at an angle of 85-90 degree into the board-to-board connector.

c). Arc down the module board until the board-to-board d connector latch engages.

2. Assemble any required thermal solution on the module after the module has been installed correctly.

Figure 5-2. Module to Connector Assembly Diagram (TBD)

To remove the module correctly, follow the installation sequence in reverse.

## **Chapter 5. Power**

Power for the module is supplied on the +5V pins and is nominally 5.0V (see the RDK X3 Module Data Sheet for supply tolerance and maximum current).

! CAUTION: RDK X3 Module is not hot-pluggable. When installing the module, the main power supply should not be connected. Before removing the module, the main power supply (to VDD\_IN pins) must be disconnected and allowed to discharge below 0.6V.

|               |                 |                   |                                      | T.T      |           |                |

|---------------|-----------------|-------------------|--------------------------------------|----------|-----------|----------------|

|               |                 | X3 Signal         |                                      | Usage on |           |                |

| Pin #         |                 |                   |                                      | RDK X3   |           |                |

|               | Module Pin Name |                   | Usage/Description                    | Module   | Direction | Pin Type       |

|               |                 |                   |                                      | Carrier  |           |                |

|               |                 |                   |                                      | Board    |           |                |

| 77,79,81,85,8 | +5V             | NA                | Main power – Supplies PMIC           | Main DC  | Input     | 5.0V           |

| 3,85,87       | +3 <b>v</b>     | INA               | and other regulators                 | input    | mput      | 5.0 V          |

|               |                 |                   | Main power – Supplies PMIC           | Main DC  |           |                |

| 104,106       | +5V             | NA                | and other regulators, always         |          | Input     | 5.0V           |

|               |                 |                   | NC;                                  | input    |           |                |

|               |                 |                   | A low on this pin forces             |          |           |                |

|               |                 | X3M_I2C4_         | booting from USB; if not used        |          |           | CMOS -         |

| 93            | nRPIBOOT        | SDA               | Leave floating. Internally           | System   | Input     | 3.3V           |

|               |                 |                   | pulled up via $4k\Omega$ to $+3.3V$  |          |           |                |

|               | RUN_PG          |                   | Module Reset. Reset to the           |          |           |                |

|               |                 |                   | module when driven                   |          | Input     |                |

|               |                 | X3M_RESE<br>TN_IN | low by the carrier board (only       | System   |           |                |

|               |                 |                   | resets the SoC                       |          |           |                |

|               |                 |                   | and eMMC device). Used as            |          |           |                |

|               |                 |                   | carrier board                        |          |           |                |

|               |                 |                   | supply enable when pulled            |          |           | CMOS –<br>3.3V |

| 92            |                 |                   | high by the module                   |          |           |                |

|               |                 |                   | When module power sequence           |          |           |                |

|               |                 |                   | is complete.                         |          |           |                |

|               |                 |                   | Used to ensure proper power          |          |           |                |

|               |                 |                   | on/off sequencing between            |          |           |                |

|               |                 |                   | module and carrier board             |          |           |                |

|               |                 |                   | supplies. $4k\Omega$ pull-up to 3.3V |          |           |                |

|               |                 |                   | on the module.                       |          |           |                |

|               |                 |                   | Input. Drive low to power off        |          |           | Open           |

| 99            | GLOBAL_EN       | NA                | Module. Internally pulled up         | System   | Input     | Drain,         |

|               |                 |                   | with a $47k\Omega$ to $+5V$          |          |           | 5.0V           |

|               |                 |                   |                                      |          |           |                |

Table 5-1. Power and System Pin Descriptions

| on the board, EMMC, Flash, | 100 | nEXTRST | X3M_RSTO<br>UT_N | Output. An active-low reset<br>output signal and generated by<br>SOC watchdog timeout event.<br>It is used to reset peripherals<br>on the board, EMMC, Flash, | System | Output | CMOS –<br>3.3V |

|----------------------------|-----|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|----------------|

|----------------------------|-----|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|----------------|

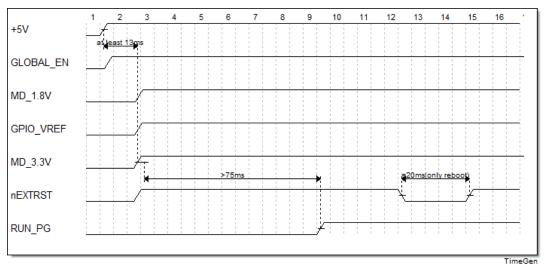

### 5.1. Power-up sequencing

The RDK X3 Module requires a single +5V power input and can supply up to 600mA at VDD\_3V3 (Pin MD\_3.3V) and VDD\_1V8 (Pin MD\_1.8V) to peripherals.

All pins should not have any power applied to them before the +5V rail is applied.

If the RDK X3 Module is to be booted using fastboot then RPI\_nBOOT needs to be low within 2ms of +5V rising.

+5V should rise monotonically to 4.8V and stay above 4.8V for the entire operation of the RDK X3 Module.

The power-up sequence will start when both +5V rail is above 4.8V and GLOBAL\_EN rises. GLOBAL\_EN has internal RC delay so that it rises after +5V has risen. The order of events is as follows:

1. +5V rises, this is the main power input.

2. GLOBAL\_EN rises, this is the enable of power supply of the module. After +5V rises, it must be kept high.

3. MD\_3.3V rises, the VDD\_3V3 output from the module. This voltage should rises at least 13ms after +5V risen.

4. RUN\_PG rises at least 75ms after MD\_3.3V, the reset signal of X3 SOC and PMIC chip. When the system finish bring up, it will be kept high.

Figure 5-1 Power-Up sequencing

Note: MD\_3.3V and MD\_1.8V are produced by the Power unit on the module. It is no need to input these power from external.

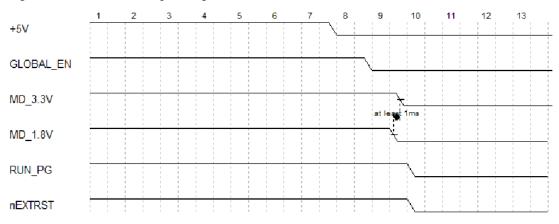

#### 5.2. Power-down sequencing

The operating system should be shut down before the power is removed, to ensure that the file system remains consistent. If this can't be achieved, then a filesystem like btrfs, f2fs or overlayfs should be considered.

Once the operating system has shut down, the +5V rail can be removed or the GLOBAL\_EN pin can be taken low to put the RDK X3 Module into the lowest power mode.

During the shutdown sequence the MD\_1.8V will be discharged before the MD\_3.3V rail. Figure 5-2 Power-down sequencing

#### 5.3. Power consumption

The exact power consumption of the RDK X3 Module will greatly depend on the tasks being run on the RDK X3 Module. The lowest shutdown power consumption mode is with the GLOBAL\_EN driven low, typically is 50µA. With GLOBAL\_EN high but software shut down, the typical consumption is 50mA. Idle power consumption is typically 200mA, but this varies considerably depending on the operating system. Operating power consumption is typically around 1.0A; again, this greatly depends on the operating system and the tasks being executed.

### 5.4. Regulator outputs

To make it easier to interface to the RDK X3 Module the on-board regulators (MD\_3.3V and MD\_1.8V) can each supply 600mA to devices connected to the RDK X3 Module. The loads on these outputs isn't taken into account in the power consumption figures.

## Chapter 6. USB

RDK X3 Module allows multiple USB 2.0, USB 3.0, interfaces to be brought out of the module. USB 3.0: 1x

See Table 6-1 for the supported USB 3.0 mapping options. These are the only options supported.

| Pin # | Module Pin Name | X3 Signal     | Usage and<br>Description                                                                                                    | Usage on RDK<br>X3 Module<br>Carrier Board | Direction | Pin Type       |

|-------|-----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------|----------------|

| 103   | USB_N           | USB_DM        | USB 2.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 105   | USB_P           | USB_DP        | USB 2.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 101   | USB_OTG_ID      | X3M_SD0_WPROT | For USB_ID<br>function. 0 (low):<br>SOC is USB<br>host, perform<br>USB host<br>operation<br>1 (high): SOC is<br>USB device. | USB ID                                     | Input     | CMOS –<br>3.3V |

| 116   | USB_RX_P        | USB_RX_P      | USB 3.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 118   | USB_RX_N        | USB_RX_M      | USB 3.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 122   | USB_TX_P        | USB_TX_P      | USB 3.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 124   | USB_TX_N        | USB_TX_M      | USB 3.0 Data                                                                                                                | USB<br>conn/device/hub                     | Bidir     | USB PHY        |

| 76    | SD0_DET_N       | X3M_SD0_DET_N | For USB Hot-<br>Plug detect. when<br>SOC is USB<br>device.                                                                  | USB<br>conn/device/hub                     | Input     | CMOS –<br>1.8V |

Notes: In the Type/Dir column, Output is from Module. Input is to Module. Bidir is for Bidirectional signals.

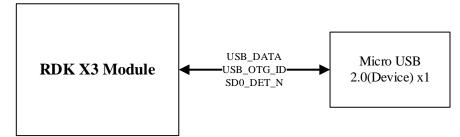

### 6.1 USB

RDK X3 Module supports up to one USB 3.0 ports. And this port also can compatible USB2.0. Note:

The example shown in Figure 6-1 is for connections to a USB device only connector to be used to support recovery mode (See Section 3.2 "USB Recovery Mode" for details on recovery mode) or a

USB device if booted normally. A USB Micro B connector is shown in the example.

Figure 6-1. USB Micro B USB Device and Recovery Connection Example

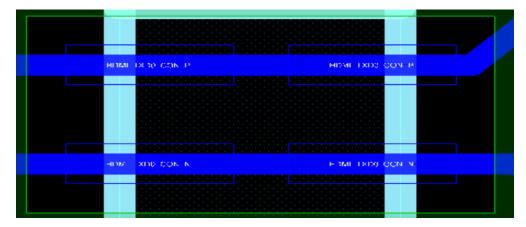

### 6.1.1 USB 2.0 Routing Guidelines

The following table details the requirements that apply to the USB 2.0 controller PHY interfaces: USB\_DM/DP.

| Parameter                                                                                                         | Requirement                                                               | Units       | Notes                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

| Max frequency (high speed): Bit Rate/UI period/Frequency                                                          | 480/2.083/240                                                             | Mbps/ns/MHz |                                                                                                                           |

| Min Pair to Pair spacing                                                                                          | Each pair should be separated by at least 3 times the signal trace width. |             |                                                                                                                           |

| Max loading: High Speed / Full Speed /<br>Low<br>Speed                                                            | 10 / 150 / 600                                                            | pF          | Max loading should<br>include any passive<br>and active<br>components on the<br>trace such<br>as CMC, Switch,<br>ESD etc. |

| Reference plane                                                                                                   | GND                                                                       |             |                                                                                                                           |

| Trace impedance: Diff pair / SE)                                                                                  | 90 / 45                                                                   | Ω           | ±10%                                                                                                                      |

| Via proximity (signal to reference)                                                                               | < 3.8 (24)                                                                | mm (ps)     | See Note 1                                                                                                                |

| Max trace length/delay<br>With CMC or SW (Microstrip / Stripline)<br>Without CMC or SW (Microstrip /<br>Stripline | 900/1050 (150)<br>1475/1720 (250)                                         | mm(ps)      | Prop delay<br>assumption: 6.9/mm<br>for stripline,<br>5.9ps/mm. for<br>microstrip. See<br>Note 3                          |

| Max intra-pair skew between USB_DM and USB_DP                                                                     | 3                                                                         | ps          |                                                                                                                           |

Table 6-2. USB 2.0 Interface Signal Routing Requirements

Notes:

1. Up to four signal vias can share a single GND return via.

2. Adjustments to the USB drive strength, slew rate, termination value settings should not be necessary, but if any are made, they

MUST be done as an offset to default values instead of overwriting those values.

#### 6.1.2 USB 3.0 Routing Guidelines

USB\_TX\_P, USB\_TX\_M, USB\_RX\_P and USB\_RX\_M. Must be designed with a differential impedance of  $90\Omega\pm10\%$ .

In order to minimize cross talk, it is recommended to keep high speed signals away from each other. Each pair should be separated by at least 5 times the signal trace width. Separating with ground as depicted will also help minimize cross talk.

Route all differential pairs on the same layer adjacent to a solid ground plane.

Do not route differential pairs over any plane split.

Adding test points will cause impedance discontinuity and will therefore negatively impact signal performance. If test point are used, they should be placed in series and symmetrically. They must not be placed in a manner that causes stub on the differential pair.

Avoid 90° turns in trace. The use of bends in differential traces should be kept to minimum. When bends are used, the number of left and right bends should be as equal as possible and the angle of the bend should be  $\geq 135^{\circ}$ . This will minimize any length mismatch causes by the bends and therefore minimize the impact bends have on EMI.

Minimize the trace lengths of the differential pair traces. The maximum recommended trace length for SuperSpeed differential pair signals and USB 2.0 differential pair signals is eight inches. Longer trace lengths require very careful routing to assure proper signal integrity.

Match the etch lengths of the differential pair traces. There should be less than 5 mils difference between a SuperSpeed differential pair signal and its complement. The USB 2.0 differential pairs should not exceed 25 mils relative trace length difference.

The etch lengths of the differential pair groups do not need to match, but all trace lengths should be minimized.

Minimize the use of vias in the differential pair paths as much as possible. If this is not practical, make sure that the same via type and placement are used for both signals in a pair. Any vias used should be placed as close as possible the module connector

## **Chapter 7. Gigabit Ethernet**

RDK X3 Module integrates a Realtek RTL8211F-CG Gigabit Ethernet controller. The magnetics and RJ45 connector would be implemented on the carrier board. Contact Realtek for carrier board placement and routing guidelines.

Table 7-1. Gigabit Ethernet Pin Description

| Pin # | Module Pin Name | X3 Signal | Usage/Description | Usage on<br>RDK X3<br>Module<br>Carrier<br>Board | Directi<br>on | Pin<br>Type |

|-------|-----------------|-----------|-------------------|--------------------------------------------------|---------------|-------------|

|-------|-----------------|-----------|-------------------|--------------------------------------------------|---------------|-------------|

| 4  | Ethernet_Pair1_P | GPHY_MDI1_P | GbE Transformer Data 1 |          |        |     |

|----|------------------|-------------|------------------------|----------|--------|-----|

| 6  | Ethernet_Pair1_N | GPHY_MDI1_N | GbE Transformer Data 1 |          |        |     |

| 3  | Ethernet_Pair3_P | GPHY_MDI3_P | GbE Transformer Data 3 |          |        |     |

| 5  | Ethernet_Pair3_N | GPHY_MDI3_N | GbE Transformer Data 3 |          | Bidir  | MDI |

| 10 | Ethernet_Pair0_N | GPHY_MDI0_N | GbE Transformer Data 0 |          | DIUII  | MDI |

| 12 | Ethernet_Pair0_P | GPHY_MDI0_P | GbE Transformer Data 0 | Not      |        |     |

| 9  | Ethernet_Pair2_N | GPHY_MDI2_N | GbE Transformer Data 2 | assigned |        |     |

| 11 | Ethernet_Pair2_P | GPHY_MDI2_P | GbE Transformer Data 3 |          |        |     |

| 15 | Ethernet nLED3   | PHY nLED3   | Ethernet 100Mbit Link  |          | input  |     |

| 15 | Ethernet_ILED5   | TIT_ILED5   | LED                    |          | mput   | -   |

| 17 | Ethernet nLED2   | PHY nLED2   | Ethernet 1Gbit Link    |          | output | -   |

| 17 | Ethemet_hEED2    |             | LED                    |          | output | -   |

Notes: In the Type/Dir column, Output is from Module. Input is to Module. Bidir is for Bidirectional signals.

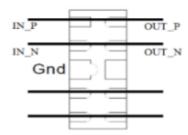

## 7.1Ethernet MDI Routing Guidelines

| The following tables describes the Ethernet signal routing requirements and connections. |

|------------------------------------------------------------------------------------------|

| Table 7-2. Ethernet MDI Interface Signal Routing Requirements                            |

| Parameter                                   | Requirement | Units                                                                                                                                         | Notes                                                                                                                                 |

|---------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Reference plane                             | GND         |                                                                                                                                               |                                                                                                                                       |

| Trace impedance Diff pair /<br>Single Ended | 100 / 50    | Ω                                                                                                                                             | <ul> <li>±15%. Differential</li> <li>impedance target is 100Ω.</li> <li>90Ω can be used if 100Ω is</li> <li>not achievable</li> </ul> |

| Min trace spacing (pair-pair)               | 0.763       | mm                                                                                                                                            |                                                                                                                                       |

| Max trace length/delay                      | 109 (690)   | mm (ps)                                                                                                                                       |                                                                                                                                       |

| Max within pair (intra-pair) skew           | 0.15 (1)    | mm (ps)                                                                                                                                       |                                                                                                                                       |

| Number of vias                              | minimum     | Ideally there should be no vias,<br>but if required for breakout to<br>Ethernet controller or magnetics,<br>keep very close to either device. |                                                                                                                                       |

Notes: X3 SOC does not support delay or skewing of clock vs. data. This must be enabled in the PHY

| Module Pin Name         | Туре     | Termination                           | Description                |

|-------------------------|----------|---------------------------------------|----------------------------|

| Ethernet_Pair [3:0]_N/P | DIFF I/O | Gigabit Ethernet MDI IF Pairs:        |                            |

| Ethemet_Fan [5.0]_WF    | DIFT I/O | Connect to Magnetics -/+ pins         |                            |

|                         |          |                                       | Gigabit Ethernet Link LED: |

|                         |          |                                       | Connect to green LED       |

| Ethernet_nLED3          | 0        | $510\Omega$ (minimum) series resistor | cathode on RJ45 connector. |

|                         |          |                                       | Anode connected to         |

|                         |          |                                       | VDD_3V3_SYS                |

| Table 7-3. Ethernet | t Signal Connections |

|---------------------|----------------------|

|---------------------|----------------------|

|                |   |                                       | Megabit Ethernet Link LED: |

|----------------|---|---------------------------------------|----------------------------|

|                |   |                                       | Connect to yellow LED      |

| Ethernet_nLED2 | 0 | $510\Omega$ (minimum) series resistor | cathode on RJ45 connector. |

|                |   |                                       | Anode connected to         |

|                |   |                                       | VDD_3V3_SYS                |

## **Chapter 8. Display**

RDK X3 Module Embedded designs can select from several display options including MIPI DSI and HDMI for external displays. The maximum number of simultaneous displays supported by RDK X3 Module is two.

### 8.1 MIPI DSI

RDK X3 Module supports three total MIPI DSI data lanes and a single clock lane. Each data lane has a peak bandwidth up to 1.5Gbps.

Table 8-1. DSI Pin Description

| Pin # | Module Pin Name | X3 Signal        | Usage/Description        | Usage on<br>RDK X3<br>Module<br>Carrier Board | Directi<br>on | Pin<br>Type |

|-------|-----------------|------------------|--------------------------|-----------------------------------------------|---------------|-------------|

| 187   | DSI1_C_N        | X3M_MIPI_DEV_CN  | Display, DSI clock       |                                               |               |             |

| 189   | DSI1_C_P        | X3M_MIPI_DEV_CP  |                          |                                               |               |             |

| 175   | DSI1_D0_N       | X3M_MIPI_DEV_D0N | Display, DSI data lane 0 |                                               |               |             |

| 177   | DSI1_D0_P       | X3M_MIPI_DEV_D0P | Display, DSI data lane 0 |                                               |               |             |

| 181   | DSI1_D1_N       | X3M_MIPI_DEV_D1N |                          | Not assigned                                  | Output        | MIPI D-     |

| 183   | DSI1_D1_P       | X3M_MIPI_DEV_D1P | Display, DSI data lane 1 |                                               |               | РНҮ         |

| 193   | DSI1_D2_N       | X3M_MIPI_DEV_D2N | Display DSI data long 2  |                                               |               |             |

| 195   | DSI1_D2_P       | X3M_MIPI_DEV_D2P | Display, DSI data lane 2 |                                               |               |             |

| 194   | DSI1_D3_N       | X3M_MIPI_DEV_D3N | Display DSI data long 2  |                                               |               |             |

| 196   | DSI1_D3_P       | X3M_MIPI_DEV_D3P | Display, DSI data lane 3 |                                               |               |             |

Notes: In the Type/Dir column, Output is from Module. Input is to Module. Bidir is for Bidirectional signals.

Notes: If EMI/ESD devices are necessary, they must be tuned to minimize impact to signal quality, which must meet the DSI spec. requirements for the frequencies supported by the design.

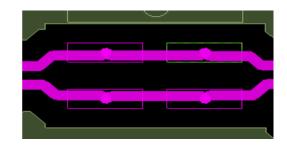

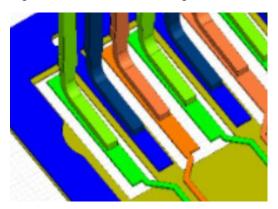

## 8.1.1 MIPI DSI and CSI Design Guidelines

| Requirement  | Units                                                                                             | Notes                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 405.5 / 811  | MHz/Mbps                                                                                          |                                                                                                                                   |

| 1            | load                                                                                              |                                                                                                                                   |

| GND          |                                                                                                   |                                                                                                                                   |

| 100 / 50     | Ω                                                                                                 | ±10%                                                                                                                              |

| < 0.65 (3.8) | mm (ps)                                                                                           |                                                                                                                                   |

| 0.15mm       | mm                                                                                                | Can be adjusted to meet Differential<br>Impedance. Loosely Coupled Diff. Pair<br>recommended by Spec.                             |

| 4x / 3x      | dielectric<br>height                                                                              |                                                                                                                                   |

| 5            | mm                                                                                                |                                                                                                                                   |

| 1100<br>800  | ps                                                                                                |                                                                                                                                   |

| 1            | ps                                                                                                |                                                                                                                                   |

| 5            | ps                                                                                                | DQ includes all the data lines associated<br>with a single clock. This may be 2<br>differential data lanes for a x2 interface, or |

|              | 405.5 / 811<br>1<br>GND<br>100 / 50<br>< 0.65 (3.8)<br>0.15mm<br>4x / 3x<br>5<br>1100<br>800<br>1 | $405.5 / 811$ MHz/Mbps         1       load         GND       Ioad         100 / 50 $\Omega$ < 0.65 (3.8)                         |

Table 8-2 details the MIPI DSI and CSI interface signal routing requirements.

## 8.1.2 MIPI DSI and CSI Connection Guidelines

| Module Pin Name | Туре     | Termination              | Description |

|-----------------|----------|--------------------------|-------------|

|                 | DIFF OUT | DSI Differential Clock:  |             |

| DGIL C N/D      |          | Connect to CLKn and      |             |

| DSI1_C_N/P      |          | CLKp pins of the primary |             |

|                 |          | DSI display              |             |

Table 8-3. MIPI DSI Signal Connections

|                 |          | DSI Differential Data       |  |

|-----------------|----------|-----------------------------|--|

|                 |          | Lanes 2:0: Connect to       |  |

| DSI1_D[2:0]_N/P | DIFF OUT | corresponding data lanes of |  |

|                 |          | DSI display.                |  |

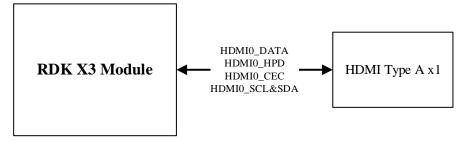

## 8.2 HDMI

A standard HDMI V1.4 interface is supported. Table 8-4. HDMI Pin Description

| Pin # | Module Pin Name | X3 Signal | Usage/Description                                                  | Usage on D-<br>Robotics Robotics<br>DevKit Carrier | Direction | Pin Type |

|-------|-----------------|-----------|--------------------------------------------------------------------|----------------------------------------------------|-----------|----------|

| 184   | HDMI0_TX0_N     | HTX0N     |                                                                    | Board                                              | Output    |          |

| 182   | HDMI0_TX0_P     | HTX0P     |                                                                    |                                                    | Output    |          |

| 178   | HDMI0_TX1_N     | HTX1N     | HDMI data lane                                                     |                                                    | Output    |          |

| 176   | HDMI0_TX1_P     | HTX1P     |                                                                    |                                                    | Output    |          |

| 172   | HDMI0_TX2_N     | HTX2N     |                                                                    |                                                    | Output    |          |

| 170   | HDMI0_TX2_P     | HTX2P     |                                                                    |                                                    | Output    |          |

| 190   | HDMI0_CLK_N     | HTXCN     |                                                                    |                                                    | Output    |          |

| 188   | HDMI0_CLK_P     | HTXCP     | HDMI clock lane                                                    | Not assigned                                       | Output    |          |

| 153   | HDMI0_HPD       | HHPD      | HDMI Port Hot<br>Plug Detect                                       |                                                    | input     |          |

| 151   | HDMI0_CEC       | HCEC      | HDMI CEC                                                           |                                                    | Bidir     |          |

| 200   | HDMI0_SCL       | HSCL      | HDMI0 SDA.<br>Internally pulled up<br>with a 1.8kΩ. 5V<br>tolerant |                                                    | Bidir     |          |

| 199   | HDMI0_SDA       | HSDA      | HDMI0 SDA.<br>Internally pulled up<br>with a 1.8kΩ. 5V<br>tolerant |                                                    | Bidir     |          |

Notes:

1. In the Type/Dir column, Output is from RDK X3 Module. Input is to RDK X3 Module. Bidir is for Bidirectional signals.

2. The directions for HHPD and HCEC are true when used for these functions. Otherwise as GPIOs, the direction is bidirectional

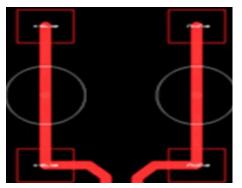

### 8.2.1 HDMI

This section shows the HDMI connection requirements, signal routing requirements, and topology. Figure 8-1. HDMI Connection Example

Notes:

1. Level shifters required on DDC/HPD. X3 pads are not 5V tolerant and cannot directly meet HDMI VIL/VIH requirements. HPD level shifter can be non-inverting or inverting. HPD level shifter on the RDK X3 Module is inverting.

| Parameter                            | Requirement                           | Units                                                     | Notes                                                                                                                   |

|--------------------------------------|---------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Topology                             | Point to point                        |                                                           | Unidirectional, differential                                                                                            |

| Termination At receiver On-<br>board | 100<br>500                            | Ω                                                         | Differential To 3.3V at<br>receiver To GND near<br>connector                                                            |

| Electrical Specification             |                                       |                                                           |                                                                                                                         |

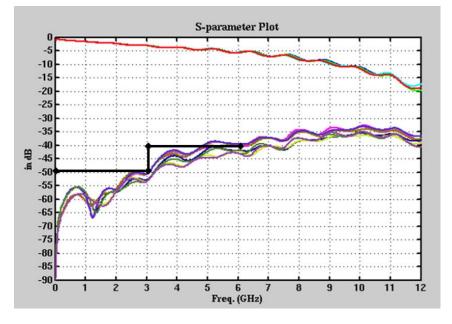

| IL resonance dip frequency           | <= 1.7<br><= 2<br><= 3<br>< 6<br>> 12 | dB @ 1GHz<br>dB @ 1.5GHz<br>dB @ 3GHz<br>dB @ 6GHz<br>GHz |                                                                                                                         |

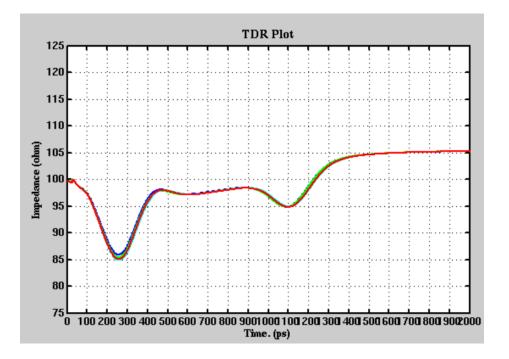

| TDR dip                              | >= 85                                 | Ω @ Tr=200ps                                              | 10%-90%. If TDR dip is<br>75~850hm that dip width<br>should < 250ps                                                     |

| FEXT (PSFEXT)                        | <= -50<br><= -40                      | dB at DC<br>dB at 3GHz                                    | PSNEXT is derived from<br>an algebraic summation of<br>the individual NEXT<br>effects on each pair by the<br>other pair |

| Parameter                            | Requirement                           | Units                                                     | Notes                                                                                                                   |

|                                      | <= -40                                | dB at 6GHz                                                |                                                                                                                         |

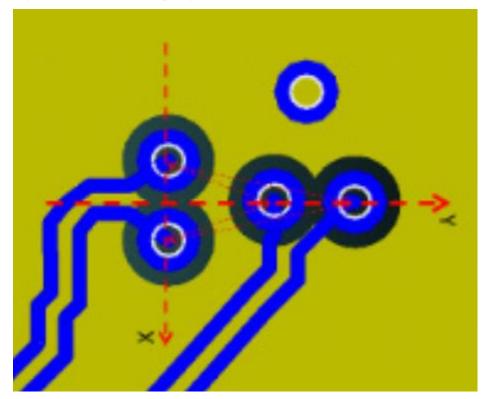

|                                      | IL/FEXT plot: See Figure 7-<br>9      |                                                           | TDR plot: See Figure 7-10                                                                                               |

| Impedance                            |                                       |                                                           |                                                                                                                         |

| Trace impedance - Diff pair          | 100                                   | Ω                                                         | $\pm 10\%$ . Target is $100\Omega$ . $95\Omega$ for the breakout and main                                               |

|                               |                          |                     | route is an implementation    |

|-------------------------------|--------------------------|---------------------|-------------------------------|

|                               |                          |                     | route is an implementation    |

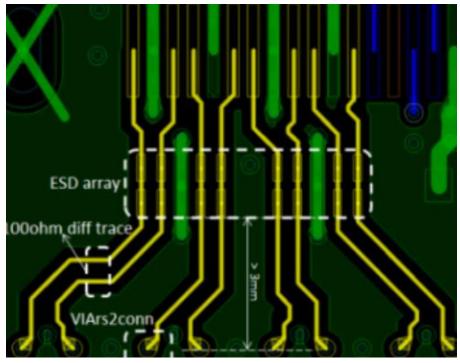

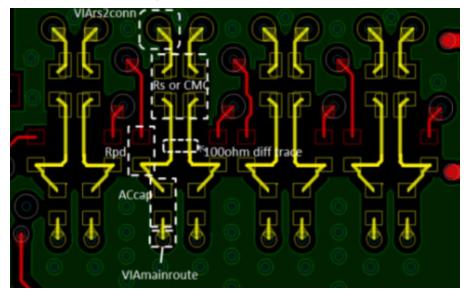

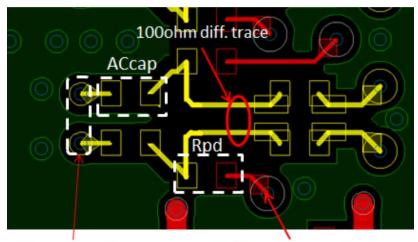

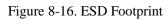

| Defense 1                     | CND                      |                     | option.                       |